計算機體系結(jié)構(gòu)中的流水線技術(shù) 邁向高性能計算系統(tǒng)集成的關(guān)鍵

在計算機體系結(jié)構(gòu)的演進歷程中,流水線技術(shù)無疑是提升處理器性能的核心技術(shù)之一。它借鑒了工業(yè)生產(chǎn)中流水線的思想,將指令執(zhí)行過程分解為多個相互獨立但又緊密銜接的階段,允許多條指令在同一時刻處于不同的執(zhí)行階段,從而顯著提高了指令吞吐率,實現(xiàn)了從串行執(zhí)行到并行處理的跨越。

流水線技術(shù)的基本原理在于將復(fù)雜的指令執(zhí)行過程細分為取指、譯碼、執(zhí)行、訪存和寫回等多個階段。每個階段由專門的硬件功能部件負責(zé),當(dāng)一條指令完成一個階段后,便進入下一個階段,同時下一條指令可以立即進入剛剛空出的階段。這種時間上的重疊,使得從宏觀上看,處理器幾乎每個時鐘周期都能完成一條指令的執(zhí)行,極大地提升了效率。經(jīng)典的5級流水線(MIPS架構(gòu))便是這一思想的典范。

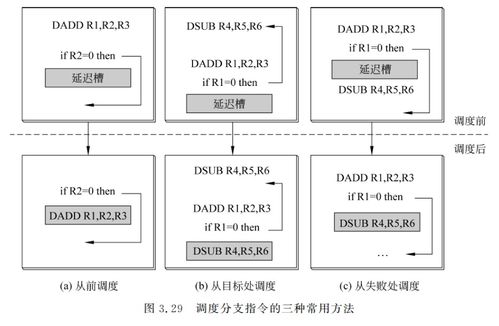

流水線的設(shè)計并非一帆風(fēng)順,其面臨的主要挑戰(zhàn)是各種“冒險”(Hazard)。結(jié)構(gòu)冒險源于硬件資源沖突,例如訪存階段單一內(nèi)存端口的爭用;數(shù)據(jù)冒險則發(fā)生在指令間存在數(shù)據(jù)依賴時,后續(xù)指令需要等待前序指令產(chǎn)生結(jié)果;控制冒險則是由分支指令引起的,處理器需要預(yù)測下一條指令的地址,預(yù)測失敗則會導(dǎo)致流水線清空,產(chǎn)生性能損失。為了解決這些問題,現(xiàn)代處理器集成了諸如轉(zhuǎn)發(fā)技術(shù)(旁路)、分支預(yù)測器、亂序執(zhí)行以及更深的流水線等復(fù)雜機制。

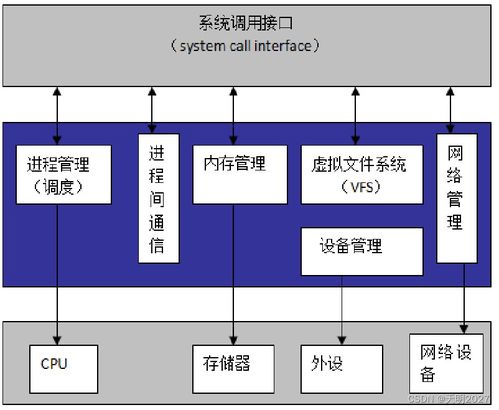

流水線技術(shù)的深度發(fā)展,直接推動了計算機系統(tǒng)的集成。在芯片內(nèi)部,更復(fù)雜、更深的流水線設(shè)計需要集成更多的功能單元、更龐大的寄存器堆和更智能的控制邏輯,這促進了微處理器內(nèi)部的高度集成與復(fù)雜化。在系統(tǒng)層面,為了充分發(fā)揮流水線處理器的性能,需要與之匹配的高速緩存(Cache)層次結(jié)構(gòu)、高帶寬內(nèi)存子系統(tǒng)以及高效的輸入輸出(I/O)通道。內(nèi)存墻(Memory Wall)問題——即處理器速度遠快于內(nèi)存訪問速度——成為系統(tǒng)集成設(shè)計中必須攻克的關(guān)鍵瓶頸。通過集成多級緩存、更寬的內(nèi)存總線和更先進的內(nèi)存技術(shù)(如DDR、HBM),系統(tǒng)設(shè)計者致力于為流水線提供持續(xù)穩(wěn)定的數(shù)據(jù)流。

流水線思想也超越了CPU本身,影響了整個計算系統(tǒng)的集成架構(gòu)。在現(xiàn)代圖形處理器(GPU)中,大規(guī)模并行流水線(流處理器陣列)是其高性能計算的基石。在網(wǎng)絡(luò)處理器和專用集成電路(ASIC)中,流水線設(shè)計也被廣泛用于實現(xiàn)高速數(shù)據(jù)包處理和特定算法加速。從單核到多核,再到眾核和異構(gòu)計算(如CPU+GPU),系統(tǒng)的集成復(fù)雜度不斷提升,其核心目標(biāo)之一就是管理好由眾多流水線核心產(chǎn)生的并行任務(wù)流和數(shù)據(jù)流。

隨著半導(dǎo)體工藝逼近物理極限,單純依靠加深流水線級數(shù)來提升頻率已面臨功耗和收益的瓶頸。未來的計算機系統(tǒng)集成將更加注重“片上系統(tǒng)”(SoC)和“異構(gòu)集成”,將CPU、GPU、AI加速器、高速互連網(wǎng)絡(luò)等通過先進的封裝技術(shù)(如Chiplet)集成在一起。在這種架構(gòu)下,流水線技術(shù)將演化為更加靈活、可配置的形態(tài),與任務(wù)調(diào)度、能效管理、存儲層次等系統(tǒng)級技術(shù)深度融合,共同支撐起下一代高性能、高能效的計算平臺。

流水線技術(shù)不僅是處理器微架構(gòu)的經(jīng)典設(shè)計,更是驅(qū)動整個計算機系統(tǒng)向更高性能、更緊密集成方向發(fā)展的核心引擎。從指令級的并行到系統(tǒng)級的協(xié)同,它深刻地塑造了現(xiàn)代計算的面貌。

如若轉(zhuǎn)載,請注明出處:http://www.childrenclothes.cn/product/73.html

更新時間:2026-02-15 14:52:56